## **EE105**

#### **Microelectronic Devices and Circuits:** MOS Large Signal Model and Bias Circuits

Prof. Ming C. Wu

wu@eecs.berkeley.edu

511 Sutardja Dai Hall (SDH)

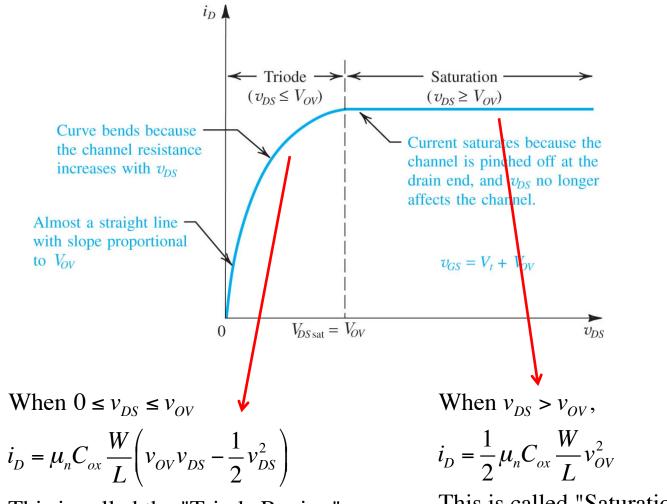

## **Saturation Region (v**<sub>DS</sub> > v<sub>OV</sub>)

This is called the "Triode Region"

This is called "Saturation Region"

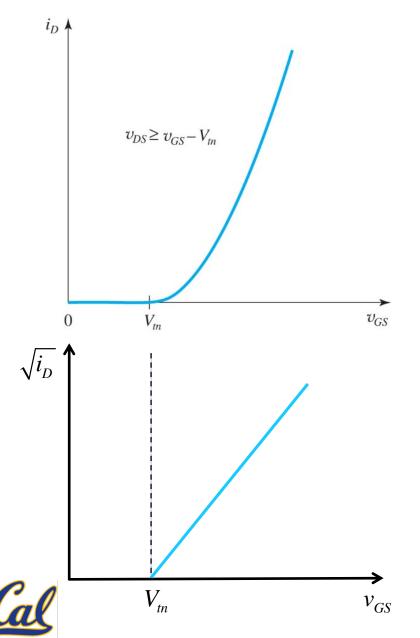

### **Drain Current vs Gate Voltage**

In Saturation Region

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} v_{OV}^2$$

$$= \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (v_{GS} - V_{tn})^2$$

To experimentally determine  $V_{tn}$ : Measure and plot  $\sqrt{i_D}$  versus  $v_{GS}$  $\sqrt{i_D} = \sqrt{\frac{1}{2}\mu_n C_{ox}\frac{W}{L}} (v_{GS} - V_{tn})$  $V_{tn}$  = intercept with horizontal axis

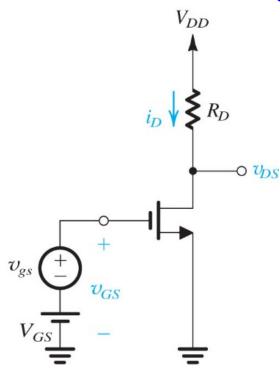

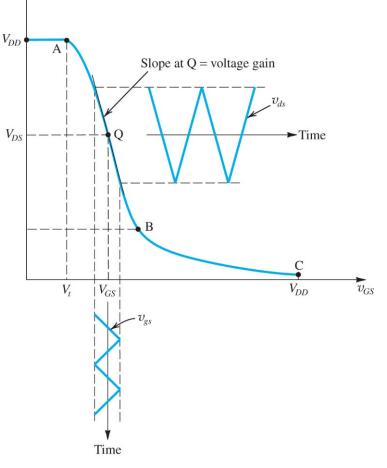

### **Analog Voltage Amplifier**

$v_{DS}$

- DC bias at Quiescent (Q) point

- Small-signal input superimposed on a DC bias voltage

- Symbol used in this course:

$$v_{GS} = V_{GS} + v_{gs}$$

Need to know the transistor's I-V characteristics to find the voltage gain (and other properties of the amplifier)

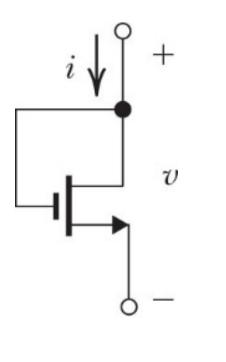

### **Diode-Connected Transistor**

With Gate connected to Drain, it becomes a 2-terminal device.This is called "diode-connected transistor"In this configuration, the transistor is always in "Saturaiton".Its I-V relationship is:

$$i = I_D = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} v_{OV}^2$$

$$v_{GS} = v_{DS} = v$$

$$v_{OV} = v_{GS} - V_{tn} = v - V_{tn}$$

$$i = \frac{1}{2}\mu_n C_{ox} \frac{W}{L} (v - V_{tn})^2$$

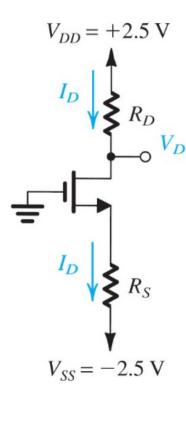

## **Example Circuit (1)**

Design Problem:

Determine  $R_s$  and  $R_D$  such that the NMOS is biased at  $I_D = 0.4mA$ and  $V_D = 0.5V$ . The NMOS has  $V_t = 0.7V$ ,  $\mu_n C_{ox} = 100 \mu A / V^2$ ,  $L = 1 \mu m$  and W =  $32 \mu m$ .

Solution:

$$R_{D} = \frac{V_{DD} - V_{D}}{I_{D}} = \frac{2.5 - 0.5}{0.4} = 5k\Omega$$

$$I_{D} = \frac{1}{2}\mu_{n}C_{ox}\frac{W}{L}v_{ov}^{2} = 0.4mA \implies v_{ov} = 0.5V$$

(channel length modulation can usually be ignored when solving DC bias)

$$v_{GS} = V_{t} + v_{ov} = 0.7 + 0.5 = 1.2V$$

$$V_{G} = 0 \text{ (grounded)} \implies V_{S} = -1.2V$$

$$R_{D} = \frac{V_{S} - V_{SS}}{I_{D}} = \frac{-1.2 - (-2.5)}{0.4} = 3.25k\Omega$$

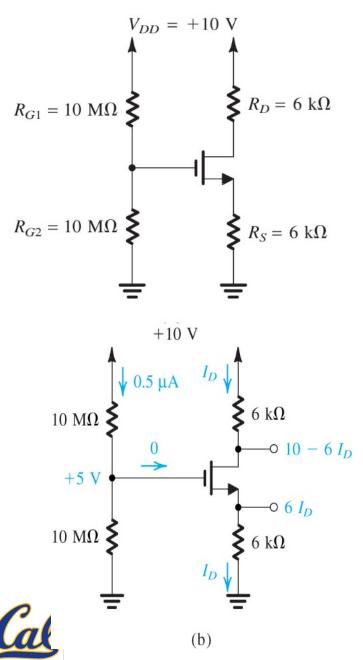

# **Example Circuit (2)**

The resistor divider is a common bias circuit. To solve the DC bias condition, it means to solve  $I_D, V_{DS}, V_{GS}$ The NMOS has  $V_{tn} = 1V$ ,  $k_n = \mu_n C_{ox} \frac{W}{I} = \frac{1mA}{V^2}$ First, solve  $V_G = V_{DD} \frac{R_{G2}}{R_{G1} + R_{G2}} = 10 \frac{5}{5 + 5} = 5V$  $V_{GS} = 5 - I_D R_S = 5 - 6I_D$  (with  $I_D$  in mA) Next, assume the transistor is in saturation:  $I_D = \frac{1}{2}k_n v_{OV}^2 = 0.5(V_{GS} - V_{tn})^2 = 0.5(5 - 6I_D - 1)^2$  $18I_D^2 - 25I_D + 8 = 0 \implies I_D = 0.89 \text{mA or } 0.5 \text{mA}$ If  $I_D = 0.89 mA$ ,  $V_{GS} = -0.34V$ , NMOS will be cut-off --> not a physical solution. If  $I_D = 0.5 \text{mA}$ ,  $V_{GS} = 2V$ ,  $V_{OV} = 2 - 1 = 1V$  $V_{DS} = V_{DD} - I_D(R_D + R_S) = 10 - 6 = 4V > V_{OV}$ Saturation assumption verified !

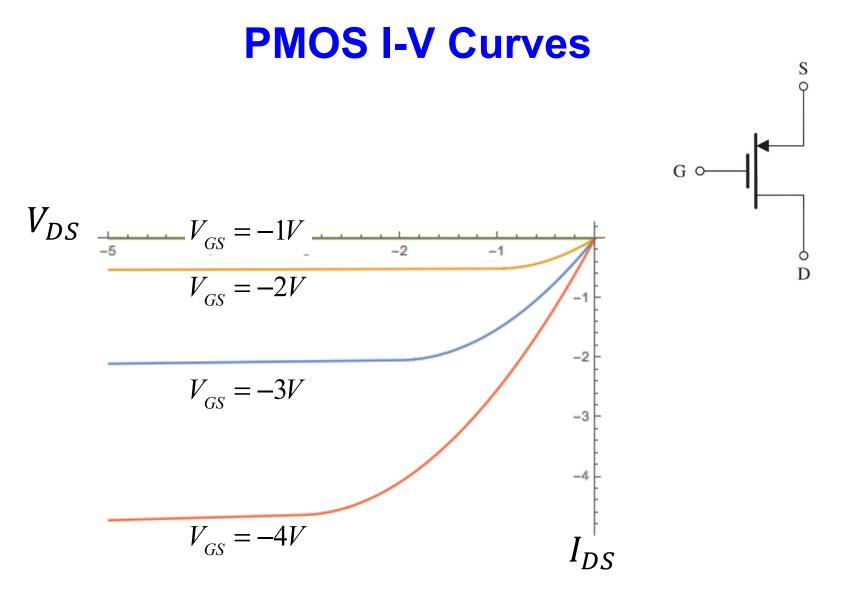

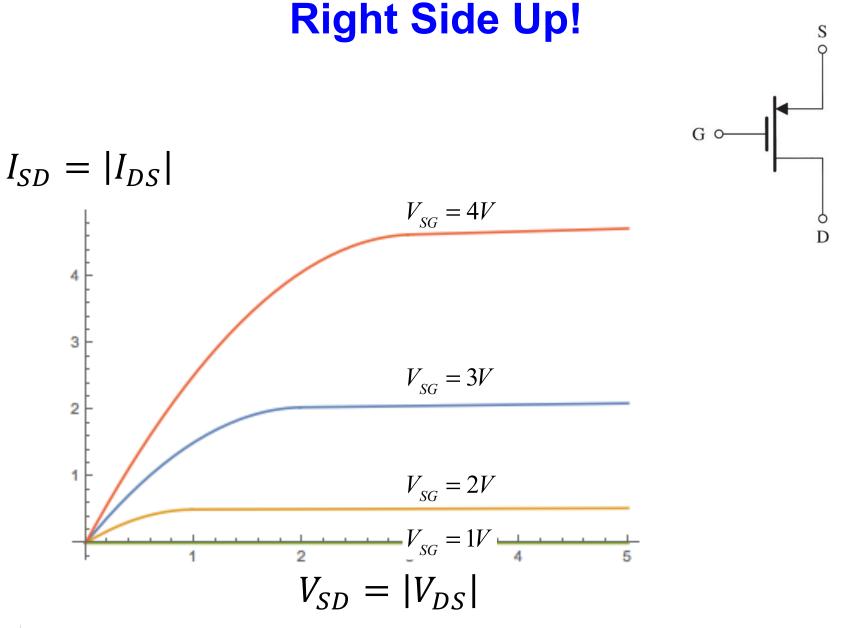

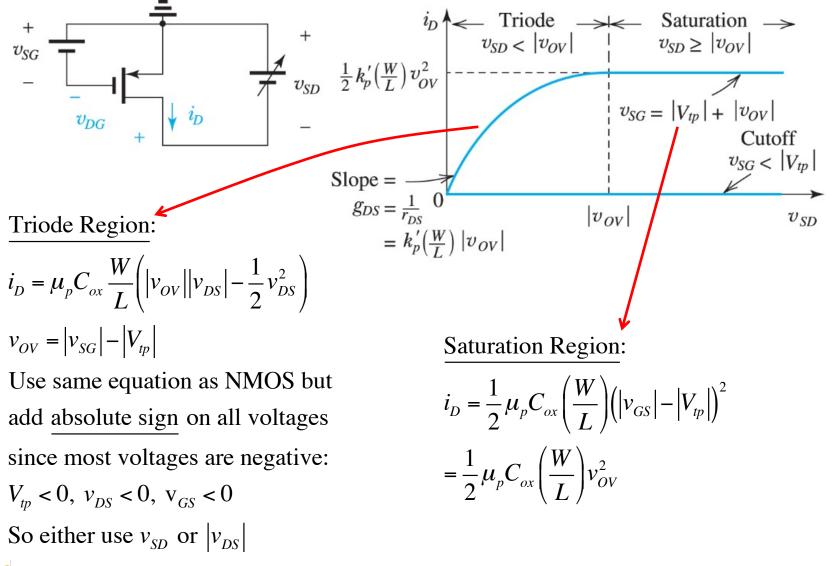

### **PMOS I-V Equations**

# **Example Circuit (3)**

$V_{DD} = +5 \text{ V}$  $R_{G1}$  $\circ V_D = +3$  $R_{G2}$  $\gtrsim R_D$  $l_D = 0.5 \text{ mA}$

Design the circuit such that  $I_D = 0.5mA$  and  $V_D = 3V$ . PMOS has  $V_{tp} = -1V$ ,  $\mu_p C_{ox}(W/L) = 1mA/V^2$ . Also find the maximum  $R_D$  for PMOS to remain in Saturation

Solution:

$$V \quad I_D = \frac{1}{2} k_p V_{OV}^2 = 0.5mA \quad \longrightarrow \quad |V_{OV}| = 1V$$

$$|V_{GS}| = |V_{tp}| + |V_{OV}| = 1 + 1 = 2V$$

$$V_S = 5V \quad \longrightarrow \quad V_G = 3V$$

We can choose  $R_{G1} = 2M\Omega$  and  $R_{G2} = 3M\Omega$

Saturation:  $V_D \le 5 - |V_{OV}| = 4V$

$$R_{D,max} = \frac{V_{D,max}}{I_D} = \frac{4}{0.5} = 8k\Omega$$

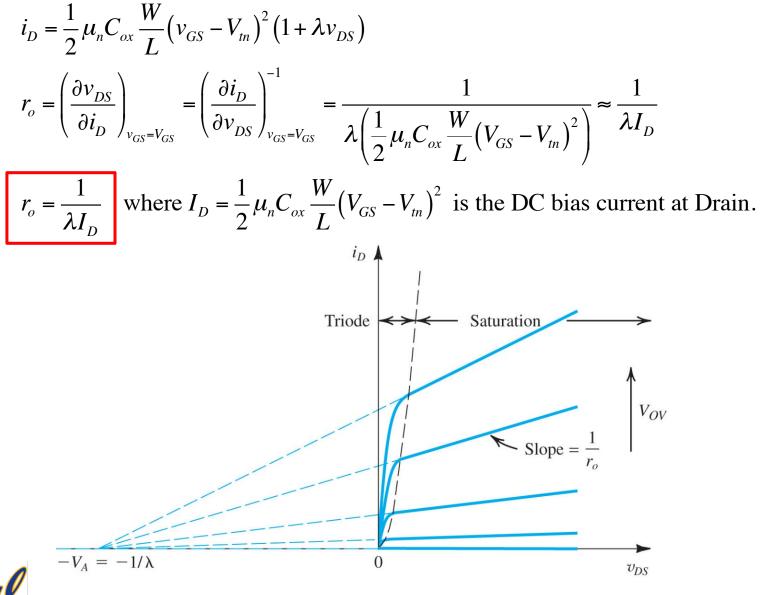

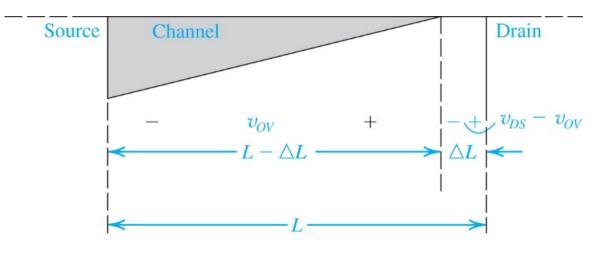

### Finite Output Resistance due to Channel Length Modulation

When  $v_{DS} = v_{OV}$ , the channel pinch of near the Drain. With further increase in  $v_{DS}$ , the pinch off point moves slowly towards the source, effectively reducing the channel length from *L* to  $L - \Delta L$  (this is called "channel length modulation"):

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L - \Delta L} (v_{GS} - V_{tn})^2$$

The continual increase of  $i_D$  with  $v_{DS}$  is modeled by

$$i_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} \left( v_{GS} - V_{tn} \right)^2 \left( 1 + \lambda v_{DS} \right)$$

#### **Output Resistance of MOSFET**